## Lecture 4

# Counters, Shift Registers & Memory

Prof Peter YK Cheung Imperial College London

URL: www.ee.ic.ac.uk/pcheung/teaching/EIE2-IAC/

E-mail: p.cheung@imperial.ac.uk

# **Learning outcomes**

- How to convert from binary to BCD format?

- How the generate various clock signals with different periods?

- How to specify shift registers?

- How to design a Linear Feedback Shift Register (LFSR) that produces pseudo-random binary sequence (PRBS)?

- How to specify ROM and RAM components?

- ❖ What is in Lab 2?

## Displaying a binary number as decimal

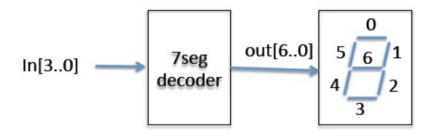

- In Lab 1 Task 4, you are required to display the counter value as binary coded decimal number instead of hexadecimal. A SystemVerilog component bin2bcd.sv is provide.

- Hex numbers are difficult to interpret. Often we would like to see the binary value displayed as decimal. For that we need to design a combinational circuit to converter from binary to binary-coded decimal. For example, the value 8'hff or 8'b1111111 is converted to 8'd255 in decimal.

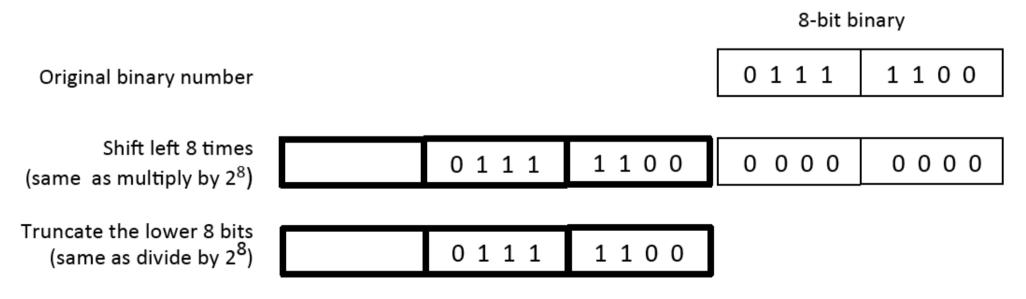

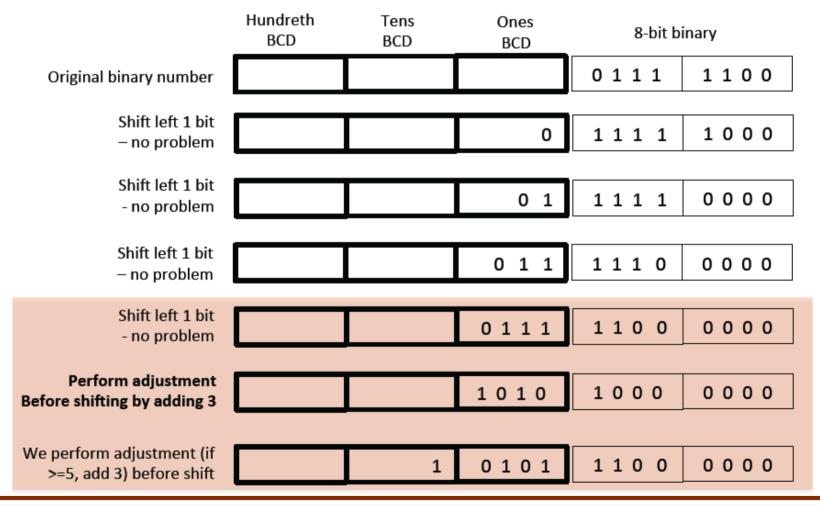

# Shift and Add 3 algorithm [1] – shifting operation

- Let us consider converting hexadecimal number 8'h7C (which is decimal 8'd124)

- Shift the 8-bit binary number left by 1 bit = multiply number by 2

- Shifting the number left 8 times = multiply number by 2<sup>8</sup>

- Now truncate the number by dropping the bottom 8 bits = divide number by  $2^8$

- ◆ So far we have done nothing to the number it has the same value

- ◆ The idea is that, as we shift the number left into the BCD digit "bins", we make the necessary adjustment to the hex number so that it conforms to the BCD rule (i.e. falls within 0 to 9, instead of 0 to 15)

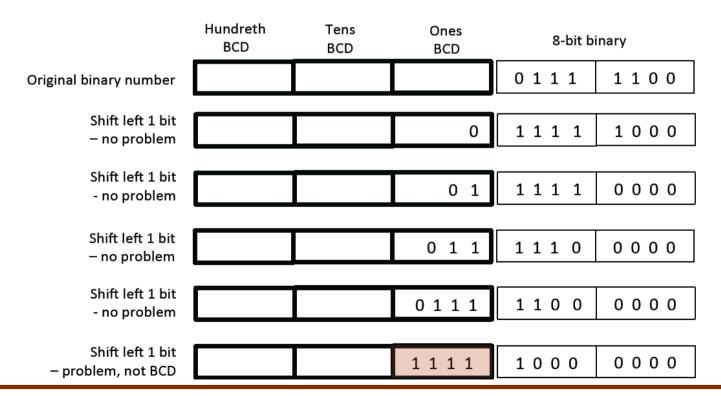

# Shift and Add 3 algorithm [2] – shift left with problem

- If we take the original 8-bit binary number and shift this three times into the BCD digit positions. After 3 shifts we are still OK, because the ones digit has a value of 3 (which is OK as a BCD digit).

- If we shift again (4<sup>th</sup> time), the digit now has a value of 7. This is still OK. However, no matter what the next bit it, another shift will make this digit illegal (either as hexadecimal "e" or "f", both not BCD).

- In our case, this will be a "f"!

# Shift and Add 3 algorithm [3] – shift and adjust

- So on the fourth shift, we detect that the value is > or = 5, then we adjust this number by adding 3 before the next shift.

- In that way, after the shift, we move a 1 into the tens BCD digit as shown here.

## Shift and Add 3 algorithm [4] – full conversion

- In summary, the basic idea is to shift the binary number left, one bit at a time, into locations reserved for the BCD results.

- Let us take the example of the binary number 8'h7C. This is being shifted into a 12-bit/3 digital BCD result of 12'd124 as shown below.

|                                     | Hundreth<br>BCD | Tens<br>BCD | Ones<br>BCD | 8-bit binary |         |

|-------------------------------------|-----------------|-------------|-------------|--------------|---------|

| Original binary number              |                 |             |             | 0 1 1 1      | 1 1 0 0 |

| Shift left three times<br>no adjust |                 |             | 0 1 1       | 1 1 1 0      | 0       |

| Shift left<br>Ones = 7, ≥5          |                 |             | 0 1 1 1     | 1 1 0 0      |         |

| Add 3                               |                 |             | 1010        | 1 1 0 0      |         |

| Shift left<br>Ones = 5              |                 | 1           | 0 1 0 1     | 1 0 0        |         |

| Add 3                               |                 | 1           | 1000        | 1 0 0        |         |

| Shift left 2 times<br>Tens = 6, ≥5  |                 | 1 1 0       | 0010        | 0            |         |

| Add 3                               |                 | 1 0 0 1     | 0010        | 0            |         |

| Shift left<br>BCD value is correct  | 1               | 0 0 1 0     | 0100        |              |         |

## SystemVerilog implementation - bin2bcd.sv

```

module bin2bcd (

input logic [7:0]

x. // value ot be converted

output logic [11:0] BCD

// BCD digits

);

// Concatenation of input and output

logic [19:0] result; // = bit in x + 4 * no of digits

integer i;

always_comb

begin

result[19:0] = 0;

result[7:0] = x;  // bottom 8 bits has input value

for (i=0; i<8; i=i+1) begin

// Check if unit digit >= 5

if (result[11:8] >= 5)

result[11:8] = result[11:8] + 4'd3;

// Check if ten digit >= 5

if (result[15:12] >= 5)

result[15:12] = result[15:12] + 4'd3;

// Shift everything left

result = result << 1;

end

// Decode output from result

BCD = result[19:8];

end

endmodule

```

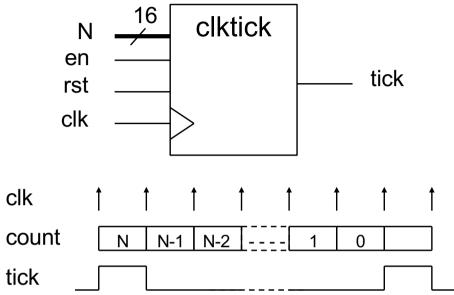

#### A Flexible Timer – clktick.sv

- Instead of having a counter that count events, we often want a counter to provide a measure of time. We call this a timer.

- Here is a useful timer component that uses a clock reference, and produces a pulse lasting for one cycle every N+1 clock cycles.

- If "en" signal is low (not enabled), the clk pulses are ignored.

```

module clktick #(

parameter WIDTH = 16

// interface signals

input

logic

clk.

// clock

logic

// reset

input

rst.

input

logic

// enable signal

en,

input logic [WIDTH-1:0] N,

// clock divided by N+1

output logic

tick

// tick output

logic [WIDTH-1:0] count;

```

#### clktick.sv explained

- "count" is an internal counter with WIDTH bits

- We use this as a down (instead of up) counter

- The counter value goes from N to 0, hence there are N+1 clock cycles for each tick pulse

```

always_ff @ (posedge clk)

if (rst) begin

tick <= 1'b0;

count <= N;

end

else if (en) begin

if (count == 0) begin

tick <= 1'b1;

count <= N;

end

else begin

tick <= 1'b0;

count <= count - 1'b1;</pre>

end

end

endmodule

```

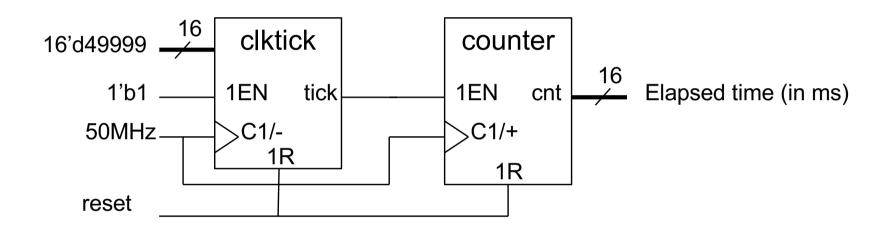

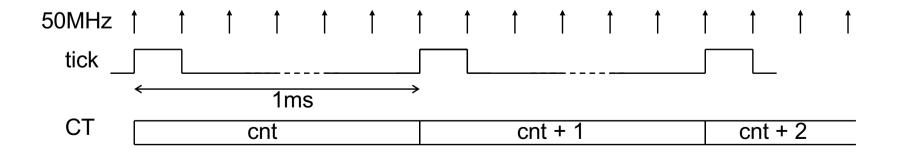

#### **Cascading counters**

By connecting clktick module in series with a counter module, we can produce a counter that counts the number of millisecond elapsed as shown below.

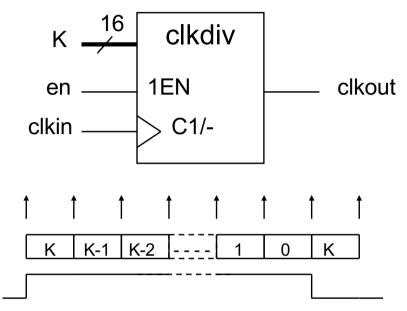

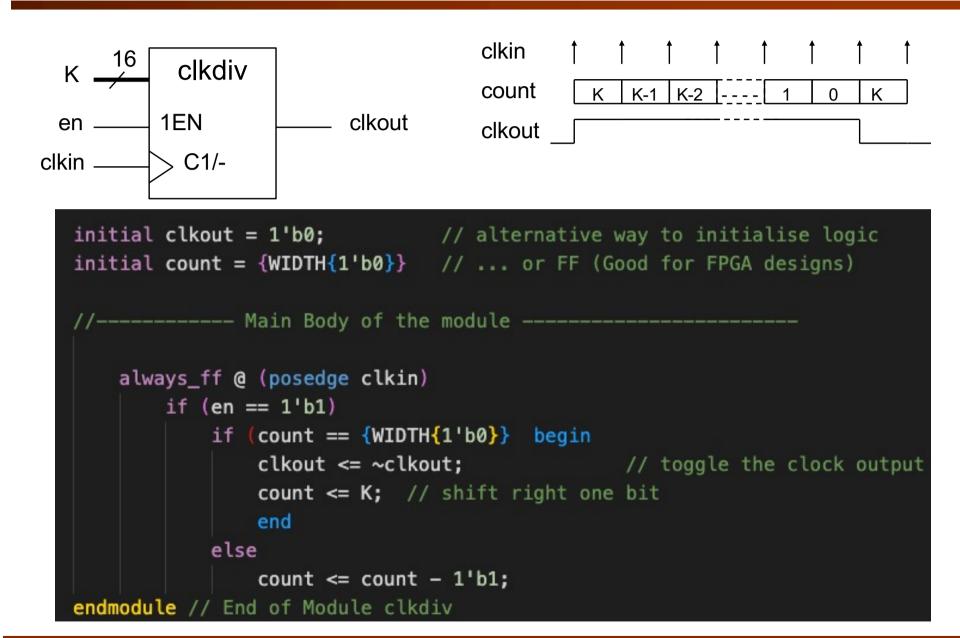

## Clock divider (clkdiv.sv)

- Another useful module is a clock divider circuit.

- This produces a symmetrical clock output, dividing the input clock frequency by a factor of 2\*(K+1).

```

module clkdiv #(

parameter WIDTH = 16

logic

clkin, // Clock input signal to be divided

input

logic

// enable clk divider when high

input

en,

logic [WIDTH-1:0] K, // half clock period counts K+1 clkin cycles

input

clkout // symmetric clock output Fout = Fin / 2*(K+1)

output logic

// End of port list

logic [WIDTH-1:0] count;

// internal counter

```

clkin

count

clkout

#### clkdiv.v explained

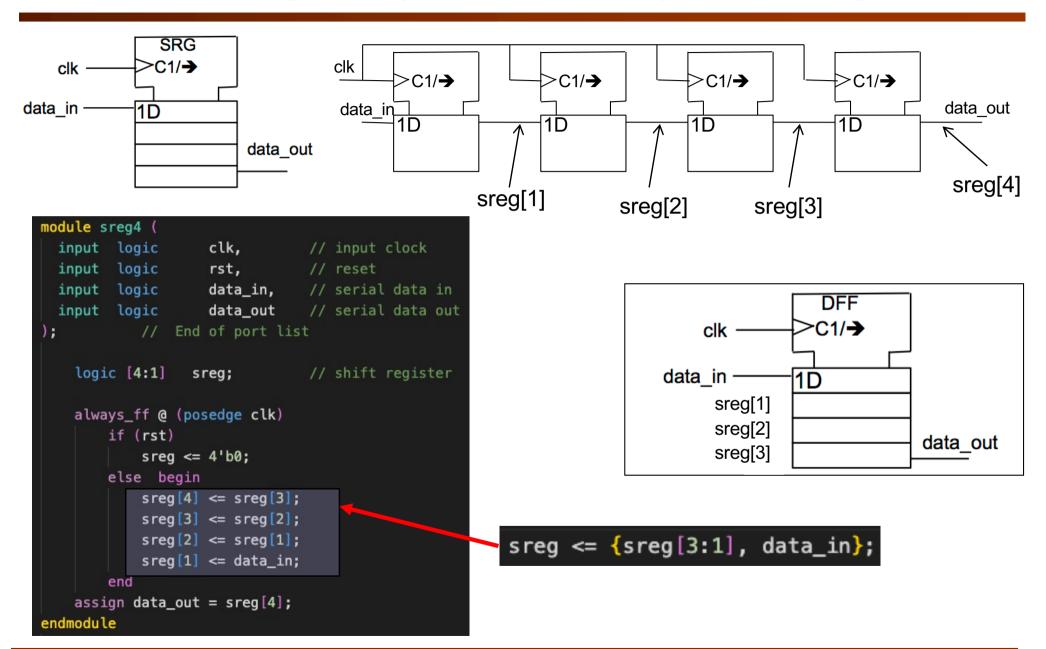

## Shift Register specification in SystemVerilog

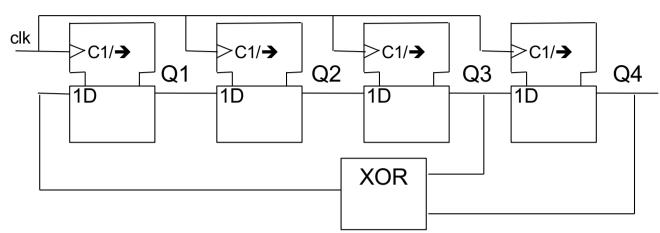

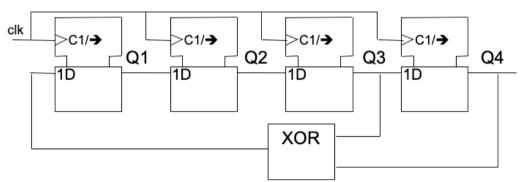

## Linear Feedback Shift Register (LFSR) (1)

- Assuming that the initial value is 4'b0001.

- This shift register counts through the sequence as shown in the table here.

- This is now acting as a 4-bit counter, whose count value appears somewhat random.

- This type of shift register circuit is called "Linear Feedback Shift Register" or LFSR.

- ♦ Its value is sort of random, but repeat very 2<sup>N</sup>-1 cycles (where N = no of bits).

- The "taps" from the shift register feeding the XOR gate(s) is defined by a polynomial as shown above.

| Q4 | Q3 | Q2 | Q1 | count |

|----|----|----|----|-------|

| 0  | 0  | 0  | 1  | 1     |

| 0  | 0  | 1  | 0  | 2     |

| 0  | 1  | 0  | 0  | 4     |

| 1  | 0  | 0  | 1  | 9     |

| 0  | 0  | 1  | 1  | 3     |

| 0  | 1  | 1  | 0  | 6     |

| 1  | 1  | 0  | 1  | 13    |

| 1  | 0  | 1  | 0  | 10    |

| 0  | 1  | 0  | 1  | 5     |

| 1  | 0  | 1  | 1  | 11    |

| 0  | 1  | 1  | 1  | 7     |

| 1  | 1  | 1  | 1  | 15    |

| 1  | 1  | 1  | 0  | 14    |

| 1  | 1  | 0  | 0  | 12    |

| 1  | 0  | 0  | 0  | 8     |

| 0  | 0  | 0  | 1  | 1     |

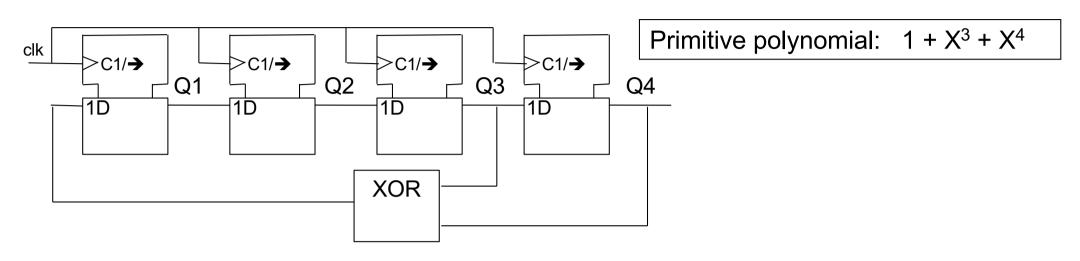

#### **Primitive Polynomial**

Primitive polynomial:  $1 + X^3 + X^4$

- This circuit implements the LFSR based on this primitive polynomial:

- ◆ The polynomial is of order 4 (highest power of x)

- ◆ This produces a pseudo random binary sequence (PRBS) of length 2⁴-1 = 15

- Here is a table showing primitive polynomials at different sizes (or orders)

| m  |                              |

|----|------------------------------|

| 3  | $1 + X + X^3$                |

| 4  | $1 + X + X^4$                |

| 5  | $1 + X^2 + X^5$              |

| 6  | 1+X+X <sup>6</sup>           |

| 7  | $1 + X^3 + X^7$              |

| 8  | $1 + X^2 + X^3 + X^4 + X^8$  |

| 9  | $1 + X^4 + X^9$              |

| 10 | $1+X^3+X^{10}$               |

| 11 | $1+X^2+X^{11}$               |

|    | 1+X+X4+X6+X12                |

| 13 | $1 + X + X^3 + X^4 + X^{13}$ |

| m  |                                 |

|----|---------------------------------|

| 14 | $1 + X + X^6 + X^{10} + X^{14}$ |

| 15 | $1 + X + X^{15}$                |

| 16 | $1 + X + X^{3+}X^{12} + X^{16}$ |

| 17 | $1+X^3+X^{17}$                  |

| 18 | $1 + X^7 + X^{18}$              |

| 19 | $1 + X + X^{2+}X^5 + X^{19}$    |

| 20 | $1 + X^3 + X^{20}$              |

| 21 | $1 + X^2 + X^{21}$              |

| 22 | $1 + X + X^{22}$                |

| 23 | $1 + X^5 + X^{23}$              |

| 24 | $1 + X + X^{2+}X^7 + X^{24}$    |

#### Ifsr4.sv

```

module lfsr4

input logic

clk,

// clock

input logic

rst,

// reset

output logic [4:1]

data_out

// pseudo-random output

);

always_ff @ (posedge clk, posedge rst)

if (rst)

sreg <= 4'b1;

else

sreg <= {sreg[3:1], sreg[4] ^ sreg[3]};</pre>

assign data_out = sreg;

endmodule

```

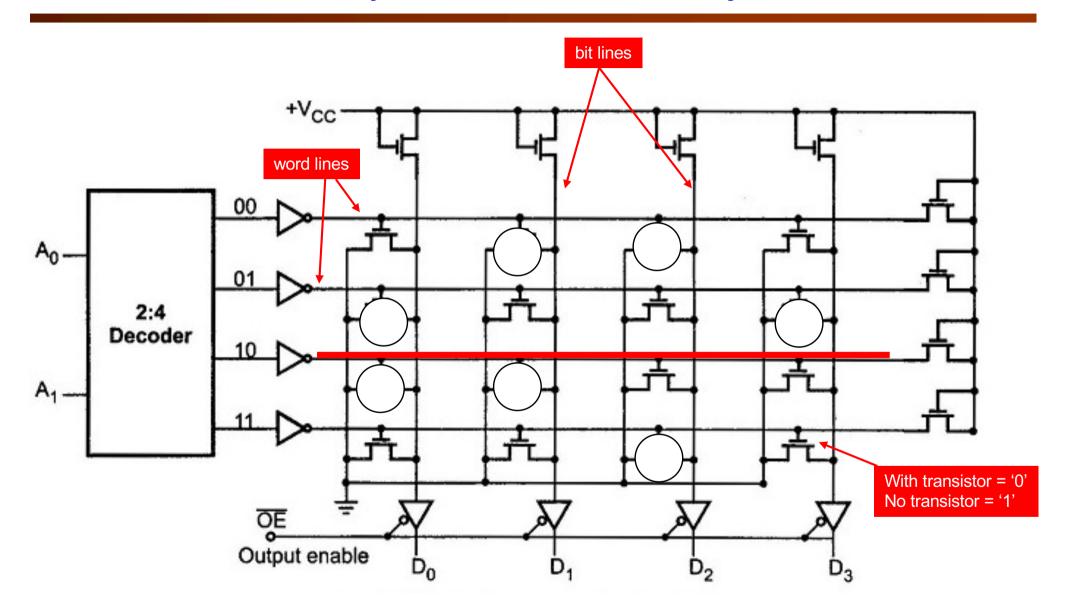

## Simplified 4 x 4 ROM array

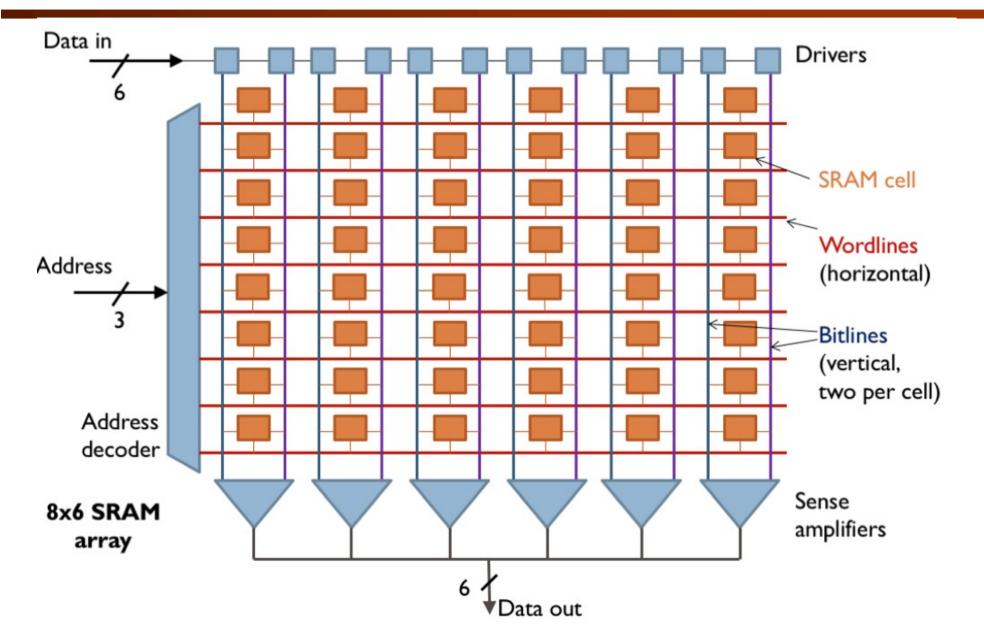

## Simplified 8 x 6 Static RAM array

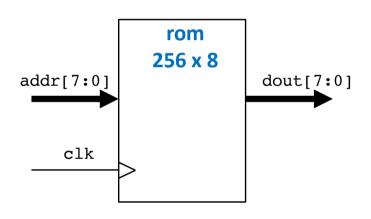

#### System Verilog specification of 256 x 8 ROM

```

module rom #(

parameter

ADDRESS_WIDTH = 8,

3

DATA_WIDTH = 8

input logic

5

clk.

input logic [ADDRESS_WIDTH-1:0] addr,

6

output logic [DATA_WIDTH-1:0]

dout

8

9

logic [DATA_WIDTH-1:0] rom_array [2**ADDRESS_WIDTH-1:0];

10

11

12

initial begin

13

$display("Loading rom.");

14

$readmemh("sinerom.mem", rom_array);

15

end;

16

always_ff @(posedge clk)

17

18

// output is synchronous

dout <= rom_array [addr];</pre>

19

20

endmodule

Verilator gives a warning unless you add an extra line!!!!!

```

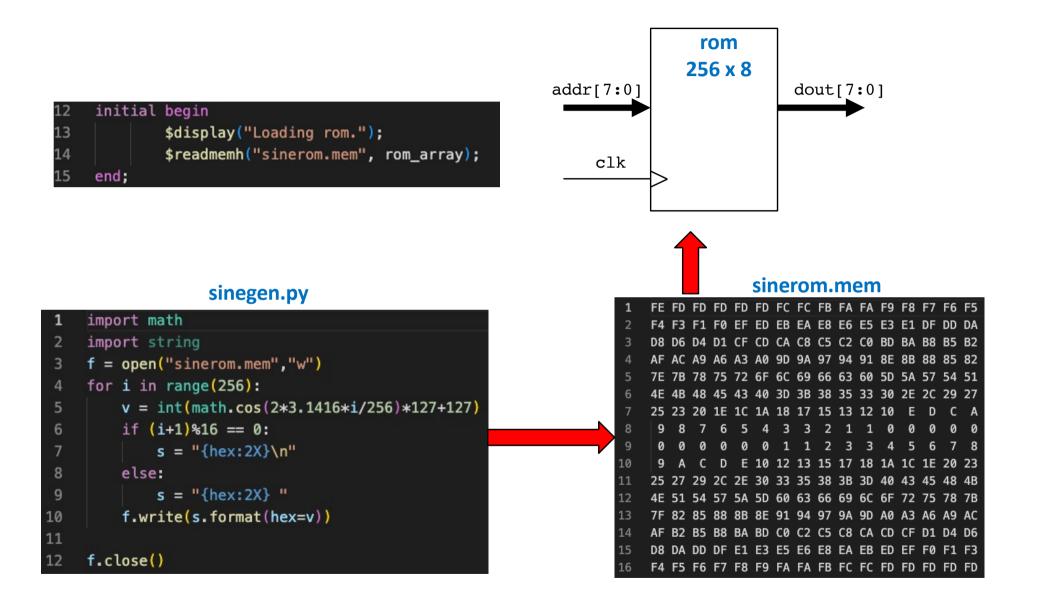

#### Initialization of the ROM

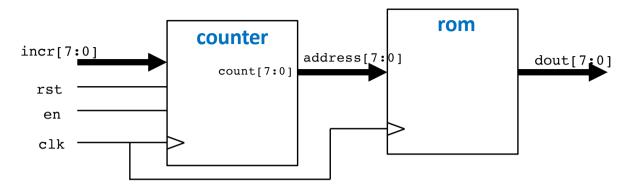

#### **Simple Sinewave Generator**

```

module sinegen #(

A_{WIDTH} = 8,

parameter

D_WIDTH = 8

input logic

clk,

rst,

input logic

en,

input logic [D_WIDTH-1:0] incr,

output logic [D_WIDTH-1:0] dout

// output data

logic [A_WIDTH-1:0]

// interconnect wire

address;

counter addrCounter (

Instantiate counter module called addrCounter

.clk (clk),

.rst (rst),

.en (en),

external signal name

.incr (incr),

.count (address)

Internal signal name

rom sineRom (

.clk (clk),

.addr (address),

.dout (dout)

```

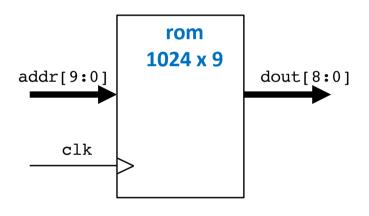

#### **Parameterised ROM:**

```

module rom #(

ADDRESS_WIDTH = 8,

parameter

3

DATA_WIDTH = 8

5

input logic

clk,

input logic [ADDRESS_WIDTH-1:0] addr,

6

output logic [DATA_WIDTH-1:0]

dout

8

logic [DATA_WIDTH-1:0] rom_array [2**ADDRESS_WIDTH-1:0];

10

11

12

initial begin

13

$display("Loading rom.");

14

$readmemh("sinerom.mem", rom_array);

15

end;

16

17

always_ff @(posedge clk)

18

// output is synchronous

dout <= rom_array [addr];</pre>

19

20

endmodule

21

```

```

rom #(10, 9) sineRom_1024x9 (....)

```

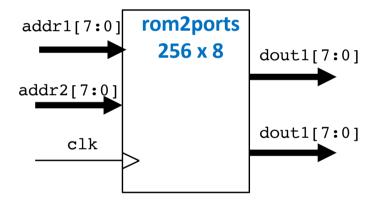

#### **Dual-port ROM**

```

module rom2ports #(

ADDRESS_WIDTH = 8,

parameter

DATA_WIDTH = 8

)(

input logic

clk.

input logic

[ADDRESS_WIDTH-1:0]

addr1,

input logic

addr2,

[ADDRESS WIDTH-1:0]

output logic [DATA_WIDTH-1:0]

8

dout1,

output logic [DATA_WIDTH-1:0]

dout2

9

10

);

11

logic [DATA_WIDTH-1:0] rom_array [2**ADDRESS_WIDTH-1:0];

12

13

initial begin

14

$display("Loading rom.");

15

$readmemh("sinerom.mem", rom_array);

17

end;

18

always_ff @(posedge clk) begin

19

// output is synchronous

20

dout1 <= rom_array [addr1];</pre>

21

22

dout2 <= rom array [addr2];</pre>

23

end

24

endmodule

```

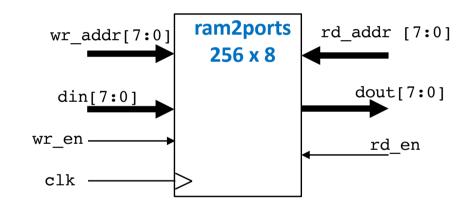

#### **Dual-port RAM**

```

module ram2ports #(

ADDRESS_WIDTH = 8,

parameter

DATA_WIDTH = 8

input logic

clk.

5

input logic

wr en,

input logic

rd en,

input logic [ADDRESS_WIDTH-1:0] wr_addr,

input logic [ADDRESS_WIDTH-1:0] rd_addr,

9

input logic [DATA_WIDTH-1:0]

din,

10

output logic [DATA_WIDTH-1:0]

11

dout

12

);

13

logic [DATA_WIDTH-1:0] ram_array [2**ADDRESS_WIDTH-1:0];

14

15

always_ff @(posedge clk) begin

16

17

if (wr_en == 1'b1)

ram_array[wr_addr] <= din;</pre>

18

if (rd_en == 1'b1)

19

// output is synchronous

20

21

dout <= ram_array [rd_addr];</pre>

22

end

endmodule

```